# Trends in Design of Low Power Circuits Using Level Shifting Buffers for Multi Supply Systems

R. Sindhu<sup>1</sup>, Katamareddy Swapna<sup>2</sup>, K. Nagendrakumar<sup>3</sup>

<sup>1</sup>Asistant professor, Vemu Institute of Technology, P. Kothakota, Andhra Pradesh, India

<sup>2</sup>Asistant professor, SVR Engineering college, Nandyal, Andhra Pradesh, India

<sup>3</sup>Assistant professor, SVR Engineering college, Nandyal, Andhra Pradesh, India

<sup>3</sup>Third Author Affiliation & Address

1sindhuadithya2017@gmail.com

2swapna.ece@svrec.ac.in

3nag.gandhi@gmail.com

Abstract- Power and performance efficiencies are the most important design parameters in system - on - chip design. Numbers of methods were developed for reducing the power and delay by reducing supply voltage and multi supply voltages. Multiple supply voltage designs need voltage level conversions between multiple voltage domains. This is achieved by the application of voltage level shifter (LS) circuits. LSs are an interfacing circuit which interconnects low core voltage to high core voltage and vice versa. LS ease communication among diverse modules. However literature reported that the conventional LSs suffer from delay variation due to dissimilar current driving transistors along with high power dissipation. This paper presents the identification of limitations and design aspects of existing LSs through an extensive literature survey and to project the current state of LSs. This study concentrates on multiple supply voltages, power consumption, and speed of processing in ICs. The detailed literature review is expected to pave way for addressing the issues and challenges related to LSs and helps in design and development of efficient low-power multivoltage LSs in the design aspects of VLSI circuits.

*Keywords* — Multi VDD systems, Power consumption, Delay, Level Shifter, IoT, Su-threshold voltage.

#### I. INTRODUCTION

The scaling in size and addition of more functional densities on digital Integrated Circuits (ICs) have given ascends to large power consumption per unit area. Power consumption of IC is one of the prominent design constraints out of speed and area. Power consumptions in VLSI are includes static, dynamic and leakage power consumption. The dynamic power consumption is a resultant of switching of load capacitance when different voltages and dependent of frequency of operation [1]. The static power is because of direct short circuit path between VDD and ground. Leakage power is due to leakage current arise from substrate-injection and sub-threshold regimes, hence enough attention can be laid on leakage power reduction. The Power consumption at system level can be reduced by scaling power supply voltage, but the problems

like voltage swing, leakage currents, and insufficient noise margins would start to originate with the supply voltage scaling and speed or delay depends on circuit topology. In view of portable and handheld devices the power consumption has turn into most significant design constraint for VLSI designers as the frequency or charging of battery back. The increase in power consumption and reliability problem also rises in addition to packaging cost. The best approach is usage of multi-VDD systems and multi VDD module are interfaced by Level shifters (LSs) and the leakage power depends on total number of MOS transistors and their operating point in spite of the switching activity [2]. LFSR counter analysis using CMOS sub-micrometer, so as to attain smaller chip size with lofty operating speeds and efficient usage of energy. From the results it is clear that the LFSR counter has additional benefits when compared to other counter parts, therefore it is a new trend setter in the field of communication for computing applications [3]. In the field of communication, energy efficient computing will play a vital role to maximize the circuit performance when we operate the device at sub threshold or near threshold regime. The effective solution to minimize the energy consumption of a circuit is MTCMOS at low power applications and GLBB is at ultra low power applications [4-5]. The results show that the proposed design achieves very good performance in terms of power and delay. The change detection and background removal application can be also realized by division operation. In image analysis, if only integer division is performed, then the results are typically rounded at the output to the next lowest integer [5].

### II. STATE OF ART LEVEL SHIFTERS

#### A. Differential Cascaded Voltage-Switch Logics LSs

A new low-power level shifter (LS) is provided for effective voltage shifting from near/sub-threshold to abovethreshold sector. The new architecture brings together the multi threshold CMOS method along with novel topological variations to assure an considerable voltage transformation, with limited energy and static power consumption. The design has implemented in 90nm technology, the proposed circuit reliably converts 0.18V input signals to 1V output signal, while maintaining signal frequency of 1 MHz, also process voltage temperature variations are considered. The Post layout simulations results demonstrates that the new LS have low propagation delay, static power dissipation, and lower energy per transition at an input voltage 0.2-V, 1 MHz pulse [6].

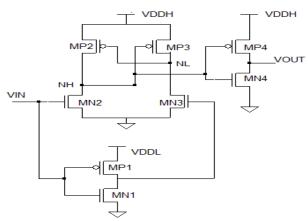

A conventional topology on voltage level shifter (VLS) for its power and delay parameters poses a special feature called built in short circuit protection, increases the speed, and reduction in power consumption is depicted in fig. 1. Unlike the available conventional LSs, the proposed VLS not requires complex digital timing signals. The VLS design was designed in CMOS 180nm process technology. The speed, power consumption of the VLS is compared with the best bench mark designs. The proposed VLS outperforms in both speed and power consumptions than the available designs. Simulation results have performed at layout extraction level and validated the design robustness [7-10].

Figure 1. Differential Cascaded Voltage-Switched Logic Level Shifters

The LS circuit described about importance of dual supply voltage design by a clustered voltage scaling (CVS) design is an efficient approach to decrease chip level power consumption. The most advantageous CVS design relies on LS implemented in a flip flop to reduce energy, delay, and area penalty due to level shifting. Moreover, circuit robustness besides supply bounce is a important property that differentiate good LS design. Two new level shifting flip-flops incorporate with half-latch type and a precharged type. These flip flops are characterized in the power delay design space to attain 30% reduction of power delay product and around 10% savings in total power of a CVS design as compared with the conventional flip flop. The projected flip flop also show 18% layout area decrease. Advantages of Level shifting in flip flop in contrast with

asynchronous level shifting are important parameters to be considered are delay penalty and its sensitivity to power supply bounce [11].

## B. Contention Mitigated Level Shifter

The design is suitable for system level Dynamic Voltage & Frequency Scaling (DVFS) environment or multiple power domain circuit blocks. In order to attain low power and high performance in IC consisting of circuit blocks having different supply voltages, the proposed design utilizes the circuit techniques for achieving less capacitive loadings signals and to reduce the contention between pull up to pull down network through positive feedback. The design performs both level up and level down shifts and are designed to perform on wide range of voltages from 0.6V to 1.6V. The new technique improve the delay and signal distortions and slew rate of signals, for verification with existing designs, the simulation is carried out at  $0.13 \mu m$ and 0.35 µm CMOS technologies. The results show that the delay and signal distortions are improved over available LSs [8], [12].

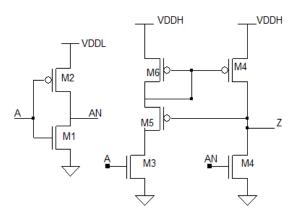

Circuit describe about importance of LS in the realization of low cost passive Radio Frequency Identification (RFID) tag, fabricated the system in a bulk CMOS process without additional process steps. RFID system memory utilizes non-volatile memory array with bit cell, consumes ultralow-power depicted in fig. 2. Cell requires the application of a 10V potential between the cell control line for program and erase operations. In this pair of voltage driver networks have introduced, that utilize novel methods to overcome these challenges. In addition, the analysis of dynamic behavior of standard level shifters has studied. This analysis has applied to GIDL free level shifters to attain optimized area, speed performance, and consumption by provide a sizing lower power methodology. The LS drivers were designed and fabricated by TowerJazz 180nm bulk CMOS process technology [22-30].

Figure 2. Contention Mitigated Level Shifter

## C. Pass Transistor Level Shifter

The Pass transistor LS have reduced the impact of normal and reverse temperature dependences on very low voltage LSs. The speed, delay, and power consumptions and variation tradeoffs on two LS designs are examined for a wide range of voltage swings. The circuit drives strengths and Process voltage Temperature corners are analyzed by using commerciality available technology tools. The developed Pass Gate level shifter is found to be better power and delay performance than the conventional DCVSL level shifter, however, limited operating range makes DCVSL is superior then pass gate type of LS [12-16].

#### D. Multi- Vth Level Shifter

The circuit developed has low-power single supply level shifter for thin oxide film transistor [16]. The developed LS circuit suitable for performing level conversion from 10V to 20V without any logic circuit, by using n-channel oxide thin film transistors. The results showed that, the level shifter operates correctly with oxide thin film transistors and the active power consumption is as low as 0.2mw at the signal frequency of 10 KHz.

Multi threshold voltage LSs are suitable for low voltage applications to change from sub-threshold to above threshold domain. They developed circuit which mixes the multi threshold CMOS methods and novel topological modifications, to guarantee wide-voltage translation range with low static power and energy consumptions. They have justified their designed work with mathematical values [17-28].

### E. Transmission Gate Level Shifting Buffer

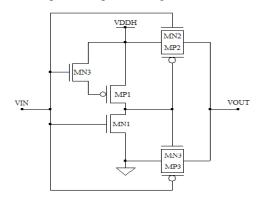

Transmission gate is the basic circuit element used in the transmission gate LS designs. Its ON resistance is less than the ON resistance of the NMOS, as ON resistance is low the lower transition times results in the output which reduces the delay and avoids contention mitigation [22]. Transmission gate LS reduces the Dynamic and leakage power consumptions, depicted in fig. 3.

Figure 3. Transmission Gate Level Shifting Buffer

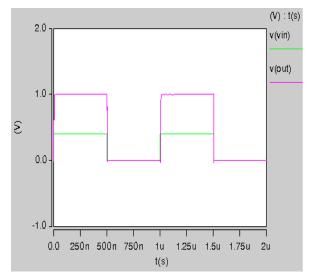

The LS operates well below sub threshold regimes. The minimum input level of the LSs is 160mV. In Fig. 4, the output node voltage (VOUT) of the Transmission Gate Level Shifting buffer is 1V. The output voltage of the LS achieves a higher value, and its slew-rate is not affected. As the output node of TG Level shifting buffer resulting in less current being supplied to the output node. A higher output value of buffer and improved output slew-rate provides the dynamic-energy efficiency and performance benefit due to current in the circuit does not need to pass for a longer time and there is no contention as well.

Figure 4. Level up shift of Transmission Gate Level Shifters

## III. COMPARATIVE ANALYSIS

Model Simulation results of the LSs for different types of topologies are depicted in table I. It can be observed that the circuit designed with TG [22] has low power consumption even at higher VDDL and its active power of 19nW at 90nm technology compare with other level shifter at the same technology [19-21]. The maximum operating frequency of the circuit is at 100 MHz also produced stable output depicted in fig. 4. The minimum values of VDDL for which the circuit operates correctly at 1 GHz are 0.11V.

Table I Comparative analysis of state art LSs

| Work/Ref. | Tech.<br>(nm) | VDDL<br>(V) | VDDH<br>(V) | Active<br>Power<br>(nW) | Delay<br>(ns) |

|-----------|---------------|-------------|-------------|-------------------------|---------------|

| [18]      | 65            | 0.16        | 1.1         | 73                      | 22.6          |

| [19]      | 90            | 0.18        | 1.2         | 91                      | 10.7          |

| [20]      | 90            | 0.14        | 1.2         | 45                      | 15.8          |

| [21]      | 90            | 0.20        | 3.0         | 151                     | 10.4          |

| [22]      | 90            | 0.23        | 1.4         | 19                      | 2.06          |

#### IV. CONCLUSION

In this brief, state of art voltage level-shifting buffer architectures was reviewed, which are able to convert very low-input voltages to above threshold voltage. The efficiency of transmission gate voltage level shifting circuit is dominating the other buffers, due to the fact that the current of pull-up device is drastically reduced while pull-down device is drastically pulling down the output node voltage, but the strength of the pull-down circuit is also drastically increased. Simulation results are strongly supporting in terms of power and performance metrics. The transmission gate voltage level shifting circuit compared with other w**O**rks, especially from the power consumption viewpoint.

#### References

- A.Wang and A. P. Chandrakasan, "A 180 mV subthreshold processor using a minimum energy circuit design methodology," *IEEE J. Solid-State Circuits*, vol. 40, no. 1, pp. 310–319, Jan. 2005

- [2] Marc Lanuzza and Stefana Perrili, "Low power LS for multi-supply voltage designs". IEEE Trans. on VLSI Systems, vol. 59. No. 12, pp. 922-926, 2012.

- [3] Srinivasulu Gundala, Venkata K. Ramanaiah, Padmapriya K. "Nanosecond Delay Level Shifter with Logic level Correction". Proceedings in International Conference on Advances in Electronics Computers and Communications (ICAECC), pp 26-30, 2014

- [4] Basha M.M., Fairooz T., Hundewale N., Reddy K.V., Pradeep B. (2012),"Implementation of LFSR Counter Using CMOS VLSI Technology", In: Das V.V., Ariwa E., Rahayu S.B. (eds) Signal Processing and Information Technology. SPIT 2011, Lecture Notes of the Institute for Computer Sciences, Social Informatics and Telecommunications Engineering, vol 62. Springer, Berlin, Heidelberg.

- [5] Srinivasulu Gundala; Venkata K. Ramanaiah; and Padmapriya K. "A Novel High Performance Dynamic Voltage Level Shifter". ARPN Journal of Engineering and Applied Sciences, 10(10), 4424-4429.

- [6] M.Mahaboob Basha, K.Venkata Ramanaiah and P. Ramana Reddy," Design of CMOS full subtractor using 10T for object detection application", International Journal of Reasoning-based Intelligent Systems (IJRIS), Vol.10, No.3/4, pp.286 – 295, 2018.

- [7] A.Manikanta, D.Y.Pushpamitra, S.Vijayakumar, "Design of CMOS PLC Receiver Using Dual Power Lines for Design For Testability", Journal of Emerging Technologies and Innovative Research, vol. 5, no. 9, pp. 74-82, 2018.

- [8] M. Mahaboob Basha, K.Venkata Ramanaiah and P. Ramana Reddy. "An efficient model for design of 64-bit High Speed Parallel Prefix VLSI adder", International Journal of Modern Engineering Research, Vol.3, Issue.5, pp.2626-2630, ISSN: 2249-6645, 2013.

- [9] Vijayakumar, S & Reeba Korah, 'Circuit level, 32 nm, 1-bit MOSSI-ULP adder: power, PDP and area efficient base cell for unsigned multiplier', IEICE Electronics Express, vol. 11, no. 6, pp. 1-7, 2014.

- [10] M. Mahaboob Basha and Jhansi Pabbathi, "Report on Ripple Carry Adder Power Delay using Brent Kung (BK) Adder", International Journal for Modern Trends in Science and Technology, 2016, Vol. 02, No. 8, pp.37-40.

- [11] Srinivasulu Gundala, Rajani Kumari, "Development Of Power And Performance Efficient 32-Bit Variable Latency Parallel Prefix

Adder", International Journal of Scientific & Technology Research, Vol. 9, No. 04, pp.3794-3798, April 2020

- [12] M.Mahaboob Basha, K.Venkata Ramanaiah, P. Ramana Reddy," Design of Near Threshold 10T- Full Subtractor Circuit for Energy Efficient Signal Processing Applications", International Journal of Image, Graphics and Signal Processing(IJIGSP), Vol.9, No.12, pp. 23-29, 2017.DOI: 10.5815/ ijigsp.2017.12.03.

- [13] Y. Osakee, and M. Numa, "A low-power LS with logic errorcorrection for extremely low voltage digital VLSI CMOS LSIS," IEEE J. Solid-State Circuits, vol. 48, no. 7, pp. 186–190, Jul. 2014

- [14] Srinivasulu Gundala, Venkata K. Ramanaiah, Padmapriya K, "Area and Energy Efficient Intelligent Level Shifter", Research Journal of Applied Sciences, Engineering and Technology, Vol.10, No. 5, pp. 532-536, 2015.

- [15] N. Md. Mohasinul Huq, M. Mahaboob Basha and Subbamma Kalingiri, "Modified CSKA Application in the Floating Point Adder using Carry Skip Adder Hybrid Structure", International Journal of Advanced Trends in Computer Science and Engineering, vol. 2, no. 8, pp.47-51, 2016.

- [16] Rajasekhara Reddy Kallam, Srinivasulu Gundala, "BlackBox Model Based VLSI Hierarchical Floorplanning", International Journal of Engineering and Advanced Technology, Vol. 8 No. 6, pp. 2604-2607 August2019.

- [17] D. Zhange and A. Alvandpaur, "A 54-nW 1-kS/s ADC in 0.13-µm CMOS medical implant devices," IEEE J. Solid-State Circuits, vol. 48, no. 7, pp. 1589–1596, Jul. 2021

- [18] Rajasekhara Reddy Kallam, Srinivasulu Gundala, "System on Chip Architecture information model based VLSI hierarchical floorplanning", International Journal of Scientific & Technology Research, Vol. 8, No. 10, pp.1471-1474, Oct 2019.

- [19] Srinivasulu Gundala; Venkata K. Ramanaiah; and Padmapriya K. "High Speed Energy Efficient Level Shifter for multi Core Processors". International Conference on Circuits, Communication, Control and Computing, Banglore, India, 393-397

- [20] Luao, C.Huuang, H. Chulu, "A wide range LS using a modified WCM hybrid buffer," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 62, no. 6, pp. 1655–1660, May 2019

- [21] S. Gundala, M. M. Basha and S. Vijayakumar, "Double Current Limiter High Performance Voltage Level Shifter for IoT Applications," 2020 5th International Conference on Communication and Electronics Systems (ICCES), 2020, pp. 285-288, doi: 10.1109/ICCES48766.2020.9137901

- [22] M.Mahaboob Basha, K.Venkata Ramanaiah and P. Ramana Reddy, "Low area- high speed - energy efficient one bit full subtractor withMTCMOS", International Journal of Applied Engineering Research, vol. 10, no. 11, pp. 27593-27604, 2015.

- [23] Mohammed Wajid Khan, S.Kaja Mohideen, S.Vijayakumar, "Design and Implementation of 1D-DCT in CORDIC Using SPST", Journal of Advanced Research in Dynamical & Control Systems, vol. 11, issue no. 1, pp. 1126-1130, 2019

- [24] B.Kaleeswari, S.Vijayakumar, Dr S Kaja Mohideen, "Optimization of Leakage Current in 8T SRAM Bit-cell at 90nm CMOS Technology-Low Power Analysis", Journal of Advanced Research in Dynamical & Control Systems, vol. 11, issue no. 1, pp. 1130-1135, 2019.

- [25] M.Sravani, S.Vijayakumar, "Design and Implementation of Hybrid LUT/Multiplexer FPGA Logic Architectures using Verilog HDL", International Journal of Research, vol. 7, no. 9, pp. 820-828, 2018.

- [26] D.Habeeba Sulthana, S.Vijayakumar, "An Efficient Implementation of High Speed, Low Power Vedic Multipliers using Reversible

Gates", Journal of Emerging Technologies and Innovative Research, vol. 5, no. 9, pp. 69-73, 2018.

- [27] N. F. Afreen, M. M. Basha and S. M. Das, "Design and implementation of area-delay-power efficient CSLA based 32-bit array multiplier", 2nd IEEE International Conference on Recent Trends in Electronics, Information & Communication Technology, pp. 1578-1582, 2017.

- [28] Konduru Lakshmi Bhanu Prakash Reddy, S.Vijayakumar, "High Speed Low Area and Energy Efficient 32 bit Carry Skip Adder using Verilog HDL", International Journal of Engineering Research in Electronics and Communication Engineering, vol. 4, no. 3, pp. 205-209, 2017.

- [29] Srinivasulu Gundala, "A Leakage Power Aware Transmission Gate Level Shifter:, International Journal of Engineering and Advanced Technology, vol. 8, no. 4, pp.1527-1530, 2019.

- [30] K. Lakshmi Bhanu Prakash Reddy, S.Vijayakumar, P.Umasankar and G. Reddy Hemantha, "High Speed, Low Area Exact Speculative Carry Look Ahead Adder using MGDI Technique", International Journal of Engineering and Advanced Technology, Volume-8, Issue-6, pp. 5090-5094, 2019.